Chiplets의 출현 • 기사 • 3D IC 이종 통합을위한 지식, 칩 렛 디자인 키트 | 지멘스 소프트웨어

Chiplet Design Kits를 사용하여 3D IC 이종 통합의 길을 닦는 데 도움이됩니다

몇 년 후, 첫 번째 프로세서는 특히 인텔 4004와 함께 나타났습니다. 그런 다음 프로세서가 더 복잡해졌습니다.

칩 렛의 출현

JZDS와 Discord에서 토론을 한 후, 나는 Chiplets에 기사를 작성하는 것이 가장 큰 숫자에 도움이 될 것이라고 스스로에게 말했습니다. 그리고 JZD에 일어날 수있는 일에 반대하는 트랙을 유지할 것입니다

아주 긴 티켓을 쓰지 않고, 나는 기사의 형식을 선호하여 세부 사항을 조금 더 얻었습니다. 나는 칩 렛이 무엇인지, 왜이 기술이 만들어 졌는지, 그리고 앞으로 몇 년 안에 발전 할 이유를 가르쳐 줄 수 있기를 바랍니다.

- 전문

- Chiplet, Quésaco ?

- 칩 렛의 경제적 측면

- 두 가지 예 : AMD와 Intel (Altera)

전문

이 기사는 특정 독자들에게 충분히 발전 할 수있는 컴퓨터의 컴퓨터, 전자 및 아키텍처 개념에 대해 이야기합니다. 나는 우리가 말하는 것을 조금 더 잘 이해하기 위해이 서문에서 약간의 대중화를 제공합니다.

순수 주의자의 경우 바로 가기가 이루어질 것입니다.이 대중화는 이해를 용이하게하기 위해 자발적으로 부정확 한 정보를 포함 할 수 있습니다.

Chiplet, Quésaco ?

가장 어려운 곳부터 시작하겠습니다 !

실제로 Chiplet이라는 용어는 1970 년대에 나타 났지만 최근 몇 년 동안 사용 된 경우, FPGA와 같은 복잡한 프로세서 나 전자 칩에 관심이있는 사람들 (내부 논리 문을 재 프로그래밍 할 수있는 칩). 다른 사람들을 위해, 방의 바닥에서, 당신은이 용어에 대해 들어 본 적이 없을 것입니다. 우리는 그것을 치료할 것입니다 !

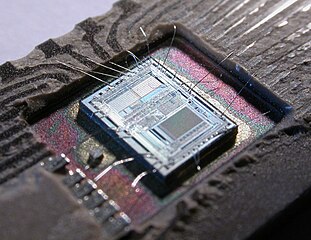

전자 칩이 무엇인지에 대한 기초로 돌아가 봅시다 : 케이스에서 캡슐화 된 새겨진 실리콘 (유명한 트랜지스터). 교차 성분을 사용하면 작은 금 또는 은색 실이 구성 요소의 다리를 실리콘 조각에 연결합니다. 처음에는 칩은 상당히 거친 해상도 (오늘과 비교)로 새겨진 트랜지스터로 구성되며 기능은 논리적 문, 작동 증폭기 등입니다. 그러나 소형화 측면에서 이미 엄청난 진전이었습니다 !

그 당시에는 구성 요소에 다리가 교차되어 있었고 실리콘 칩을이 다리에 연결해야합니다. 칩과 케이스 내부의 다리 사이에 용접되는 얇은 은색 또는 금으로 만들어졌습니다.

몇 년 후, 첫 번째 프로세서는 특히 인텔 4004와 함께 나타났습니다. 그런 다음 프로세서가 더 복잡해졌습니다.

1970 년대부터 IBM은 MCM 구성 요소를 개발했습니다멀티 코디) 단일 케이스에 여러 실리콘 칩을 포함합니다. 그러나이 기술은 주로 90 년대 후반에 발전 할 것입니다. 우리는 1995 년에 출시 된 인텔의 펜티엄 프로에 주목할 수 있습니다. 이 프로세서에는 두 개의 실리콘 칩이 포함되어 있습니다. 하나는 프로세서 용으로, 하나는 엄격하게 말하면 L2 캐시 메모리 (프로세서와 RAM 사이의 버퍼 메모리, 프로세서에 새겨 져 있기 때문에 훨씬 빠르지 만 훨씬 비쌉니다).

사진에서 볼 수 있듯이 두 칩은 대략 같은 크기를 가지고 있으며 Intel은 여러 크기의 캐시 L2를 제공했습니다. 캐시 메모리 프로세서를 분리하는 이점은 케이스에 다른 크기 칩을 넣어 다른 캐시 메모리 크기를 제공하면서 프로세서 칩에서 스케일을 저장할 수 있다는 것이 었습니다.

IBM이 MCM 구성 요소를 계속 개발하더라도 이러한 유형의 구성 요소는 비교적 저개발 상태로 남아 있습니다. 2004 년에 출시 된 IBM의 Power5는 캐시 L3 메모리 칩으로 4 개의 프로세서가 정사각형으로 나타납니다. 벼룩의 상호 연결은 케이스 내부에서 수행됩니다.

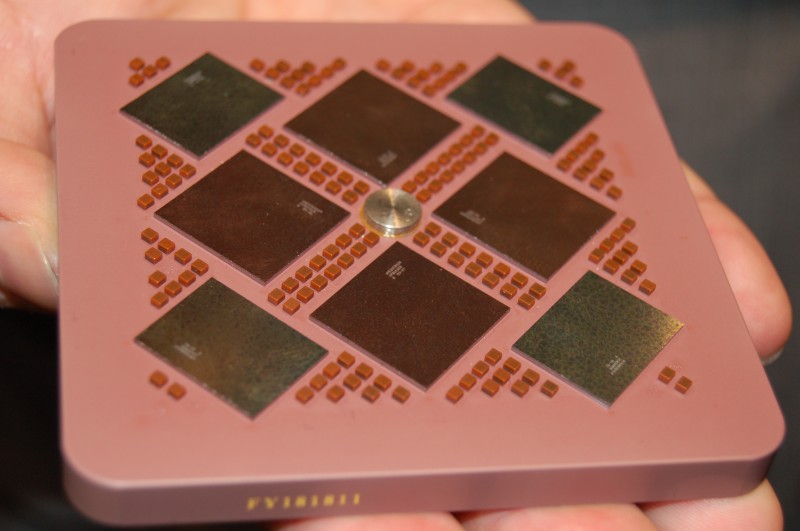

오늘날 기술이 발전했으며 MCM 칩은 AMD 프로세서가있는 소비자 제품에 있습니다. 여기서는 9 개의 상호 연결된 실리콘 칩으로 구성된 EPYC 7702 프로세서 (2019 년 8 월에 출시)를 볼 수 있습니다. 코어와 캐시 메모리가 포함 된 8 칩과 다른 8을 연결하는 중앙 칩 및 신호 D ‘입구/ DDR을 관리하는 중앙 칩을 볼 수 있습니다. 종료 (SATA, PCI Express, USB 등.))).

하지만 멍청이는 무엇입니까? ?

아 네, 조금 파생되었습니다

실제로 칩 렛은 MCM에 존재하는 실리콘 칩 중 하나입니다. 칩 렛은 다른 칩 렛과 상호 연결되도록 만들어졌습니다. 예, 비교적 간단하지만 이해하기 위해 멋진 사진을 보여 주어야했습니다

그럼에도 불구하고 Chiplets의 의미에 대해 조금 더 정확하다는 아이디어는 반드시 여러 다른 칩을 연결하는 것이 아닙니다. 재사용 할 수 있고 특정 프로세서 참조에 전념하지 않는 일반 칩의 개념도 있습니다.

칩 렛의 경제적 측면

이 소개 후 이미지가있는 동안, 이제 Chiplets가 미래에 왜 발전할지 이해해 봅시다. 이를 위해서는 전자 벼룩 제조 과정으로 돌아갈 필요가 있습니다.

모래 해변에서 여행이 길어서 안락 의자에 편안하게 앉아

아니, 잠깐 !

우리는 실리콘 제조의 전체 부분을 보낼 것입니다. 우리에게 관심이있는 것은 벼룩 분포입니다주사위) 실리콘 케이크에 (웨이퍼)) 및 특히 조각품의 증가에 따른 수율의 진화.

그러나 수율의 이러한 측면 전에, 우리는 다이의 최대 물리적 크기에 대해 이야기해야합니다. 실제로 실리콘 팬케이크에서 칩의 동일한 디자인이 여러 번 반복됩니다 (수십 또는 수백 번). 이 디자인의 인상은 자외선을 통해 광학적으로 이루어집니다. 그러나 전체 렌즈와 광학 메커니즘 세트가 있습니다.

벼룩을 복잡하게할수록 트랜지스터를 더 많이 넣고 싶으므로 칩의 크기를 늘리거나 같은 표면에 더 많은 트랜지스터에 맞게 조각의 진미를 증가시켜야합니다. 그러나 다른 제약과 한계도 느껴집니다.

이것이 칩 렛의 원리가 이러한 한계를 우회하는 데 흥미로운 이유입니다. 함께 연결된 몇 개의 작은 실리 쿰 칩을 사용하여 더 복잡한 칩을 만들지 만 모 놀리 식으로 인해 조각하는 것은 불가능합니다.

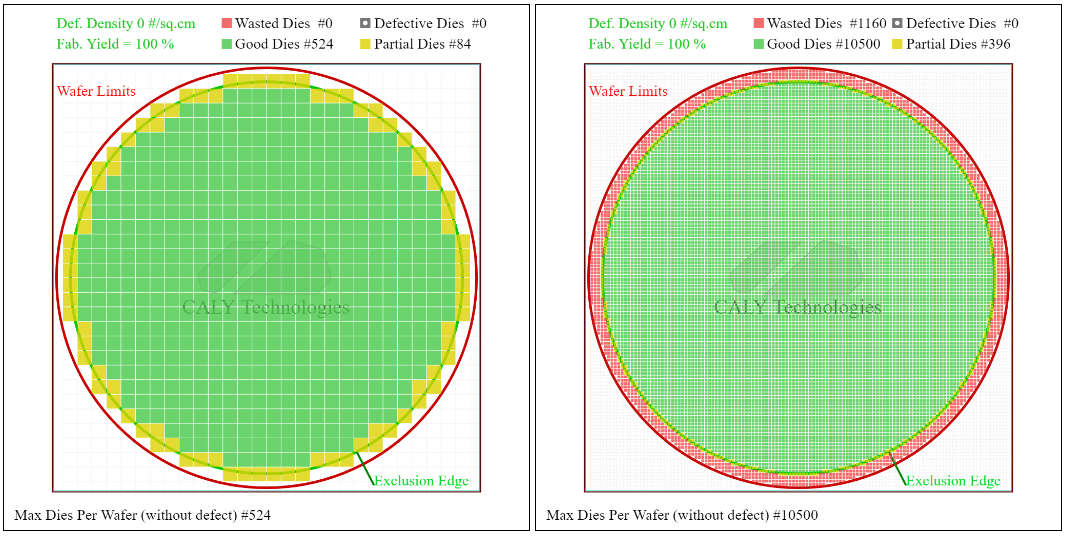

이제 수율로 돌아 가기 (생산하다 영어로). 먼저, 웨이퍼는 모양이 둥글고 우리는 직사각형 칩으로 그것을 좋아합니다. 전체 실리콘은 사용되지 않습니다. 그러나 가장자리에서 죽을수록 우리는 전체 죽을수록 더 많이 가질 수 있습니다. 비디오 게임에서 별명과 같은 원칙입니다. 둥근 모양을 형성하는 데 사용되는 픽셀이 작고 닉킹을 덜 알 수 있습니다.

위의 예에서, 총 다이 수 (양호 및 바이어스)의 부분 다이를보고하면 13의 비율을 얻습니다.5 × 5 mm 및 3의 다이의 경우 8 %.1 × 1 mm 다이의 경우 6 %. 다이가 작을수록 가장 유효한 다이가 가장자리에 가질 수있어 수율이 증가합니다.

또한 웨이퍼 중앙에 큰 다이 혼합물을 만들고 가장자리에서 작은 다이를 사용하여 별명으로 인해 수율을 최적화 할 수 있습니다.

Jamy라고 말하면, 왜 우리는 둥근 웨이퍼를 사용하여 직사각형 벼룩을 만들까요? ?

글쎄, 그것은 실린더 형태의 실리콘을 제공하는 czochralski 공정이라는 실리콘을 만드는 방법 때문입니다 웨이퍼.

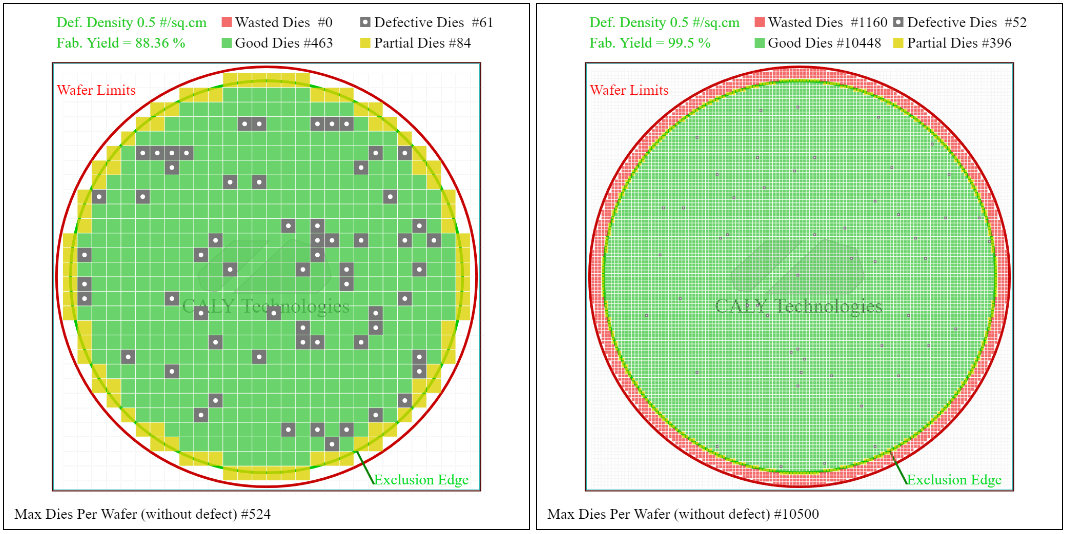

둘째, 수율은 웨이퍼에 나타날 수있는 결함의 영향을받습니다. 웨이퍼에 떨어지는 먼지 곡물을 생각할 수 있습니다.

0의 결함 밀도를 추가하여 이전 예제를 재개했습니다.cm² 당 5. 이제 비교하십시오 수율 제조 기능 다이 수와 생산 된 총 제품 수 사이의 비율에 해당합니다. 5 × 5 mm 다이의 경우 수율은 88입니다.4 % 1 × 1 mm 다이에서 수율은 99입니다.5 %.

따라서 전자 벼룩 생산을 최적화하기 위해 작은 다이를 갖는 것은 이중으로 흥미 롭습니다. 그럼에도 불구하고 복잡한 칩을 여러 개의 작은 칩으로 자르려면 이러한 다른 칩을 그들 사이에 전달해야합니다. 따라서 추가 공간을 차지하고 추가 에너지를 사용하는 통신 요소를 추가해야합니다.

또한, 칩 렛을 사용하면 최종 칩의 비용을 성능으로 조절할 수있는 기능에 따라 다른 조각의 사망의 다이를 사용할 수 있습니다.

마지막으로, 또 다른 경제적 측면은 새로운 기능을 개발하는 복잡성입니다. 이것은 사용 준비가 된 지적 재산 블록 (기능)을 제공하는 전문 회사 (또는 적어도 시작시 신생 기업)를 갖는 경향이 있습니다. 예를 들어, 프로세서 제조업체는 PCI Express, USB 또는 DDR 컨트롤러와 같은 기능을위한 다이를 구매하는 동안 프로세서 자체의 개발에 집중할 수 있습니다.

다른 제조업체에서 나오는 칩 렛의 상호 운용성을 용이하게하기 위해 Intel, AMD, ARM, Qualcomm, Samsung 또는 TSMC와 같은 주요 플레이어Universal Chiplet Interconnect Express))).

두 가지 예 : AMD와 Intel (Altera)

amd epyc

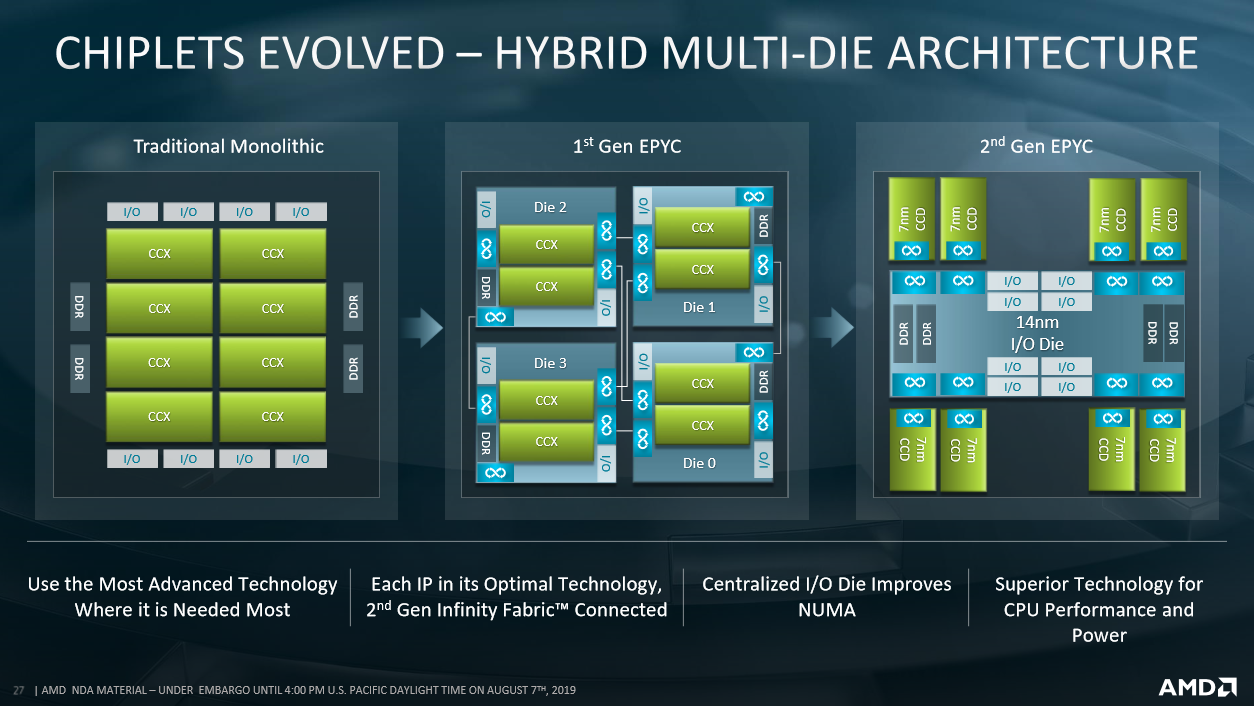

오늘날 점점 더 많은 프로세서 가이 Chiplets 기술을 사용합니다. AMD는 1 세대 EPYC 프로세서 이후 칩 렛을 사용합니다인피니티 패브릭.

1 세대의 EPYC 프로세서는 완전한 프로세서가 함께 연결되는 일련의 다이를 보았습니다인피니티 패브릭 최종 프로세서를 형성합니다. 따라서 Chiplets는 일종의 작은 자율 프로세서였습니다. 각 다이는 항목/출력을 관리하고 DDR 컨트롤러가있었습니다.

이 죽음, 또는 오히려 칩 렛에는 두 가지가 있습니다 핵심 컴퓨팅 단지 (CCX, 캐시 메모리가있는 4 개의 코어 세트)와 DDR 컨트롤러는 입력/출력 (예 : PCI Express)을 관리하며인피니티 패브릭.

작은 미묘함, 1 세대 epyc에는 항상 4 개의 칩 렛이 있습니다. 마음의 수를 변화시키기 위해 AMD는 CCX 내부의 하트를 비활성화합니다. 예를 들어 24 개의 코어가 있으시면 CCX에는 3 개의 활성 코어 만 있습니다

따라서이 1 세대는 큰 모 놀리 식 다이를 개발하는 대신 일종의 사본/접착제로 칩 렛의 원리를 사용했습니다.

2 세대의 경우 AMD는 개념을 조금 더 밀어냅니다. 실제로 CCX는 이제 독립적이며 핵심 컴퓨팅 다이 (CCD) 연결 인피니티 패브릭 DDR 및 호출 항목/출구를 관리하는 다이에 I/O 다이 (IOD).

AMD는 기능과의 분리를 완전히 활용합니다. 실제로 CCD는 7 nm로 새겨 져 있으며 ioD는 14 nm로 새겨 져 있습니다.

epyc 프로세서의 칩 렛에있는 구절을 요약 한 AMD 프레젠테이션 아래.

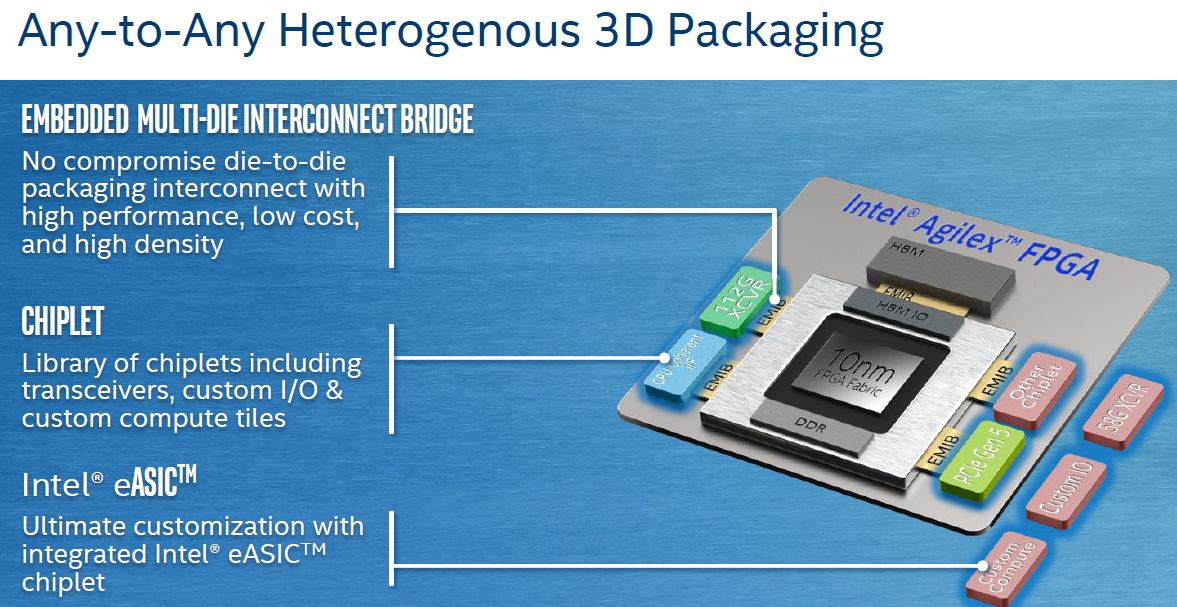

인텔 FPGA (Altera)

인텔 프로세서는이 기사의 시작 부분에서 볼 수있는 몇 가지 예외를 제외하고는 항상 모 놀리 식 칩입니다. 그럼에도 불구하고 인텔 FPGA (재구성 가능한 FPGA) 부문에서는 최신 세대에 Chiplets를 사용합니다.

이 칩 렛은 주로 사용 된 트랜스커니 유형 (빠른 링크)에 관한 것이며 타일. 인텔 이이 타일에서 사전 정의 된 범위를 제공하는 경우 자신의 요구에 맞는 맞춤형 칩을 가질 수 있어야합니다.

타일은 트랜시버의 최대 속도와 지원되는 프로토콜 (이더넷, PCI Express 등)으로 나뉩니다.) : P의 경우 16g, H의 경우 28g, R의 경우 32g 등.

인텔은 또한 미래를 위해 추가 기능을 제공 할 맞춤형 칩 렛을 연결할 가능성을 불러 일으 킵니다. 현재 회사는 ADC/DAC (Jariett Technologies) Chiplet과 다른 광학 연결 (Ayar Labs)을 출시했습니다.

마지막으로 우리는 칩을 믿어서는 안됩니다 단단히 짜여 하나로 되어 있는 죽었다. 그들은 항상 내부 통신 및 대기 시간 측면에서 항상 장점이 있으며, 이는 대형 칩이 필요한 특정 응용 프로그램에 중요 할 수 있습니다.

이 비디오에서 디자이너가 선택한 Broadcom과 그 스위치 400G 칩의 경우입니다 : https : // www.YouTube.com/watch?v = b-cogmbaug4

이 기사가 당신에게 더 많은 것을 가지고 있기를 바랍니다. 나는 복잡한 주제를 대중화하려고 노력했지만 첫 번째 단락 이후에 당신을 지킬 수 있기를 바랍니다

특정 요점이 당신을 위해 비밀스러운 상태로 남아 있다면 주저하지 말고 세부 사항을 제공하려고 노력할 것입니다.

6 댓글

이 답변은 유용했습니다

훌륭한 기사, 감사합니다 @ Zeql !

“나를 늑대에게 던지면 나는 팩을 반환 할 것이다.” – 세네카

이 답변은 유용했습니다

나는 칩 렛의 출현이 하드웨어에서 어떤 진화를 고려할 수 있었는지 궁금했다 소비자 등급 저것 서버 등급) 미래에, 또는 전체적으로 최적의 기계를 설계하는 방식으로 패러다임 전환.

특정 통합 시스템 (특히 Apple). 스마트 폰으로 제한된 시스템에서 H265 트랜스 코딩 칩, AI의 계산 장치를 찾을 수 있습니다사과 신경 엔진) 그리고 물론 고전적인 그래픽 단위.

따라서 2 세대 AMD EPYC의 다이어그램을 취하고 칩 렛이 특정 작업에서 최적의 성능을 달성하기 위해 여러 특수 칩을 착수하는 완전한 유닛에서 상업적으로나 산업적으로 실행 가능한 간단한 방법인지 궁금합니다. 예를 들어, 장치는 클래식 CCD를 제공 할 수 있지만 DSP, GPU, Transco H265/AV1/VP9/…, AES 등을 수행하는 칩 등을 제공 할 수 있습니다. IOD/Infinity Manufacture를 통해 모든 것을 연결하십시오. 따라서 각 기계/서버 제조업체는 R & D/Faramineurous 산업화 비용없이 자체적으로 구성하여 즉시 사용 가능한 최종 장치를 구성 할 수 있습니다.

APU의 개념을 생각 나게하지만 보고서가 있는지 모르겠습니다.

이 답변은 유용했습니다

나는 칩 렛의 출현이 하드웨어에서 어떤 진화를 고려할 수 있었는지 궁금했다 소비자 등급 저것 서버 등급) 미래에, 또는 전체적으로 최적의 기계를 설계하는 방식으로 패러다임 전환.

특정 통합 시스템 (특히 Apple). 스마트 폰으로 제한된 시스템에서 H265 트랜스 코딩 칩, AI의 계산 장치를 찾을 수 있습니다사과 신경 엔진) 그리고 물론 고전적인 그래픽 단위.

따라서 2 세대 AMD EPYC의 다이어그램을 취하고 칩 렛이 특정 작업에서 최적의 성능을 달성하기 위해 여러 특수 칩을 착수하는 완전한 유닛에서 상업적으로나 산업적으로 실행 가능한 간단한 방법인지 궁금합니다. 예를 들어, 장치는 클래식 CCD를 제공 할 수 있지만 DSP, GPU, Transco H265/AV1/VP9/…, AES 등을 수행하는 칩 등을 제공 할 수 있습니다. IOD/Infinity Manufacture를 통해 모든 것을 연결하십시오. 따라서 각 기계/서버 제조업체는 R & D/Faramineurous 산업화 비용없이 자체적으로 구성하여 즉시 사용 가능한 최종 장치를 구성 할 수 있습니다.

APU의 개념을 생각 나게하지만 보고서가 있는지 모르겠습니다.

따라서 칩은 종종 IP (지적 재산)로 수행된다는 것을 알아야합니다. “트랜지스터”레벨에서 상당히 준비된 기능은 설계에 통합되어야합니다.

전형적인 예는 -Board 마이크로 컨트롤러의 DDR3 컨트롤러입니다. 마이크로 컨트롤러 제조업체는 반드시 DDR3을 마스터 할 필요는 없으며 DDR3 컨트롤러를 생성하려는 시간 (욕구가 아님)이 아닙니다. 따라서 그는 컨트롤러에서 IP를 구매하고 그를 디자인에 통합합니다.

IP의 가능성과 칩 렛의 차이를 보는 데 성공해야합니다. 나에게 칩 렛이 와서 하나 이상의 고급 기능을 가져오고 이미 조각의 테스트를 통과 했으므로 디자인의 추가 단계입니다. 그러나 모든 칩 렛으로 전체 토양을 테스트하는 문제가 남아 있습니다. 그래서 우리는 레고와 같은 수백 가지 변형을 만들 수 없습니다. 최소한의 경제 현실이 필요합니다.

그러나 그렇습니다. 특정 볼륨의 경우 à la carte 소켓을 만들 수 있습니다.

큰 장점은 칩의 생산 측면에 있습니다. 다른 조각 칩에 대해 다른 조각 칩에 대한 IP가 감소 할 수 있다면 다른 부품 칩이 할 수있는 경우 초기 세분 (충분한 경우)에 항상 새겨 질 수 있다는 이점을 얻을 수 있습니다. 더 작은 조각으로 개선됩니다.

이 답변은 유용했습니다

게다가 나는 칩 렛이 모듈 식 디자인에 사용될 수 있다고 생각했다. 당신은 4 개의 칩으로 디자인을하고, 결함이있는 벼룩은 생산 전반에 걸쳐 분포되며, 4 개의 칩이있는 것은 4 개의 칩이 아래에 있으며 그 작동하는 4 개가있는 것보다 약간 저렴합니다.

기존 운영과 관련하여 설계 및 산업화를 단순화하는.

무료 소프트웨어의 애호가 및 GNU/Linux Fedora 배포. #Jesuisarius

이 답변은 유용했습니다

이 흥미로운 메가 기사에 감사드립니다. 나는 당신이 튜토리얼에서 설명하지 않는 각 요점을 설명하기 위해 너무 많은 시간을 당신에게 사랑하지만 어쨌든 흥미 롭습니다 .

Chiplet Design Kits를 사용하여 3D IC 이종 통합의 길을 닦는 데 도움이됩니다

Chiplet은 다른 칩 렛과 함께 패키지 내에서 작동하도록 특정으로 설계되고 최적화 된 ASIC 다이입니다. 이기종 통합 (HI). 이 장치는 성능, 전력, 지역, 비용 및 TTM을 포함하여 고려 가능한 혜택으로 제공됩니다.

Chiplet Design Exchange (CDX)는 EDA 공급 업체, Chiplet으로 구성됩니다

제공 업체/어셈블러 및 SIP 통합 자이며 칩 렛 생태계를 용이하게하기 위해 표준화 된 칩 렛 모델 및 워크 플로우를 추천하는 개방형 작업 그룹입니다. 이 웨비나는 2 개의 칩 렛 디자인 키트 (CDK) 제안을 요약하여 2를 표준화하는 데 도움이됩니다.5d 및 3.D IC 디자인은 개방 된 생태계를 만들기위한 설계.

성공을위한 생태계 구축 2.5D 및 3D Chiplet 모델 통합

SOC 프로세스와 유사하게 칩 플레트를위한 생태계가 필요합니다. 주요 시장 채택 및 Chiplet 기반 설계의 주요 시장 채택 및 배치를위한 키가 포함됩니다

- 기술 : 2.5 D 개입 및 3D 스택 다이 제조 및 조립 공정

- IP : 표준화 된 칩 렛 모델

- 워크 플로 : EDA 디자인 흐름 및 PDK, CDK, DRM 및 어셈블리 규칙

- 비즈니스 모델 : Chiplet Marketplace

CDX의 초기 초점은 2입니다.3D가있는 5D 개재 기반 칩 렛 모델. 웹 세미나에서 이러한 노력에 대해 자세히 알아보십시오.

Chiplet Design Exchange (CDX)는 EDA 공급 업체, Chiplet 제공 업체/어셈블러 및 SIP 통합 자로 구성되며 칩 렛 생태계를 용이하게하기 위해 표준화 된 칩 렛 모델 및 워크 플로우를 추천하는 개방형 작업 그룹입니다. 이 웨비나는 2 개의 칩 렛 디자인 키트 (CDK) 제안을 요약하여 2를 표준화하는 데 도움이됩니다.5d 및 3.D IC 디자인은 개방 된 생태계를 만들기위한 설계.

성공을위한 생태계 구축 2.5D 및 3D Chiplet 모델 통합

SOC 프로세스와 유사하게 칩 플레트를위한 생태계가 필요합니다. 주요 시장 채택 및 Chiplet 기반 설계의 주요 시장 채택 및 배치를위한 키가 포함됩니다

- 기술 : 2.5 D 개입 및 3D 스택 다이 제조 및 조립 공정

- IP : 표준화 된 칩 렛 모델

- 워크 플로 : EDA 디자인 흐름 및 PDK, CDK, DRM 및 어셈블리 규칙

- 비즈니스 모델 : Chiplet Marketplace

CDX의 초기 초점은 2입니다.3D가있는 5D 개재 기반 칩 렛 모델. 웹 세미나에서 이러한 노력에 대해 자세히 알아보십시오.

유출 된 이미지는 GPU AMD Radeon을위한 야심 찬 칩 렛 디자인을 보여줍니다

유출 된 이미지는 GPU AMD Radeon을위한 야심 찬 칩 렛 디자인을 보여줍니다

- ~에 의해

- 뉴스에서

- 2023 년 8 월 16 일

유출 된 이미지가 표면화되어 Navi 4C Chip 4C의 취소 된 프로젝트에서 Radeon Chiplets로 GPU 디자인을 드러 냈습니다. 단일 GPU에 13 ~ 20 개의 다른 칩 렛 사이에있는 디자인은 야심 찬 AMD 접근법을 증언합니다. 이 복잡한 칩 렛 디자인은 현재 Radeon RX 7900 XTX에 사용되는 NAVI 31 실리콘과 다릅니다. GPU의 이전 반복은 1 세대로 간주되었지만 AMD의 최근 Ryzen 프로세서와 같은 실제 칩 렛 디자인을 사용하지 않았습니다. 그러나 NAVI 4C의 개념은 단일 기판에 여러 계산 칩 렛과 별개의 I/O 칩 렛을 포함하기 때문에 상당한 발전을 나타냅니다. 누출 된 이미지는 13 개의 칩 렛을 나타냅니다. 이미지에 추가 메모리 컨트롤러 칩이 표시되지 않을 가능성이 있습니다.

이미지의 진위를 확인하려면 병렬 프로세서의 모듈성 개념을 논의하는 2021의 관련 특허가 강조 표시됩니다. 특허 패턴은 누출 된 이미지에 표시된 디자인과 매우 유사하며 횡단 컵의 다른쪽에 더 많은 칩 렛의 가능성을 제안합니다.

불행히도 유출 된 이미지에 제시된 GPU의 디자인이 취소되었습니다. 이는 차세대 GPU에 대한 AMD의 악센트가 NAVI 43 및 NAVI 44 모 놀리 식 칩에 고급 구성 요소가 아닌 일반 대중을 대상으로 할 것이라는 최근의 관계에 동의합니다. 그러나 AMD는 미래의 그래픽 카드의 고급 세그먼트, 잠재적으로 RDNA 5와 함께 여러 계산 칩 렛으로 구성된 GPU의 개발에 대한 노력을 리디렉션하는 것으로 추측됩니다.

게임 그래픽에 대한 몇 가지 계산 칩 렛의 실현은 기존 CPU 계산보다 더 복잡하지만 AMD의 디자인 장애물을 극복하고 RDNA 5에 대한 더 나은 솔루션을 사용하기로 한 AMD의 결정은 긍정적 인 단계로 인식됩니다. AMD가 개선 된 NAVI 31의 새로운 노드와 같은 구조 계획을 갖는 것이 유리했을 것입니다.